Vitis Unified Software Platform

- Developer Tools

- Software Tools

- Vitis Software Platform

Vitis™ Unified Software Platform Overview

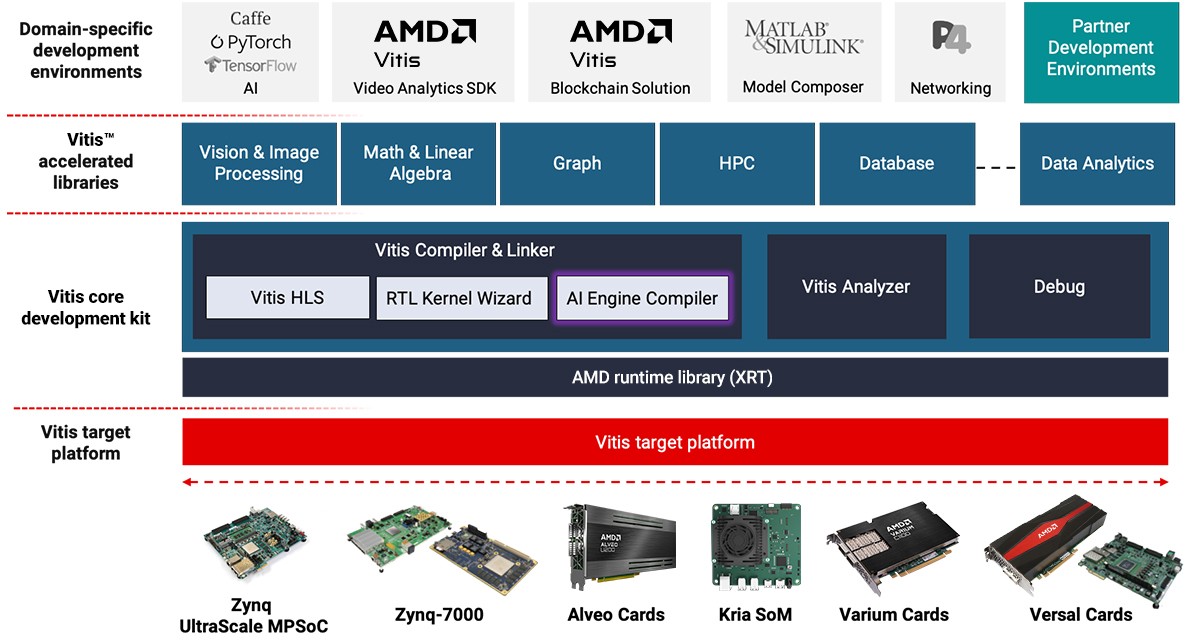

The Vitis unified software platform includes:

- A comprehensive core development kit to seamlessly build accelerated applications

- A rich set of hardware-accelerated open-source libraries optimized for AMD FPGA and Versal™ adaptive SoC hardware platforms

- Plug-in domain-specific development environments enabling development directly in familiar, higher-level frameworks

- A growing ecosystem of hardware-accelerated partner libraries and pre-built applications

- Vitis Model Composer, a model-based design tool that enables rapid design exploration and verification within the MathWorks MATLAB® and Simulink® environment and accelerates the path to production on AMD devices.

- Vitis Networking P4, which allows for the creation of soft-defined networks. The VitisNetP4 data plane builder generates systems that can be programmed for a wide range of packet processing functions - from simple packet classification to complex packet editing.

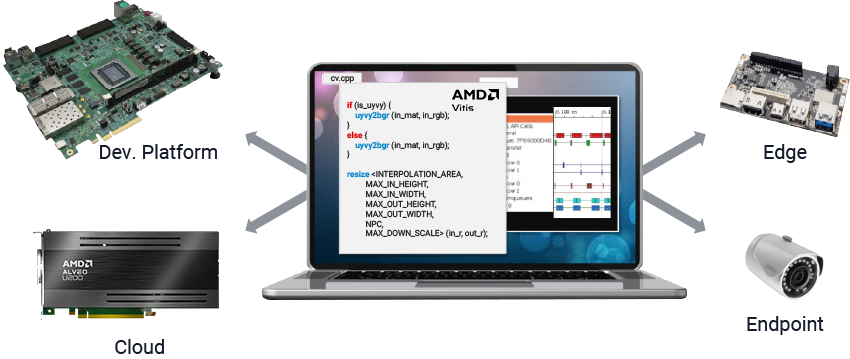

Platform-Based Flow

Development in the Vitis environment enables portability from platform to platform, whether you are porting from a proof of concept, a development kit, or a custom board.

The Vitis platform-based design methodology provides many productivity advantages:

- Platform reuse: Swap different acceleration applications with the same platform

- Application portability: Port applications across different platforms with minimum effort

- Simulation time: Speed up co-simulation with kernels

- Run time: Open-source run time that takes care of host-device communication through a PCIe® or an embedded interface

- System debug: Save full hardware compile by co-simulating the full system

Key Components of the Vitis Unified Software Platform

Vitis AI Development Environment

The Vitis AI development environment is a specialized development environment for accelerating AI inference on AMD embedded platforms, Alveo accelerator cards, or on the FPGA-instances in the cloud. Vitis AI development environment supports the leading deep learning frameworks like Tensorflow and Caffe, and offers comprehensive APIs to prune, quantize, optimize, and compile your trained networks to help achieve the highest AI inference performance for your deployed application.

Vitis Accelerated Libraries

Open-source, performance-optimized libraries that offer out-of-the-box acceleration with minimal to zero-code changes to your existing applications, written in C, C++ or Python. Leverage the domain-specific accelerated libraries as-is, modify to suit your requirements or use as algorithmic building blocks in your custom accelerators.

Vitis Core Development Kit

A complete set of graphical and command-line developer tools that include the Vitis compilers, analyzers, and debuggers to build applications, analyze performance bottlenecks, and debug accelerated algorithms, developed in C, C++, or OpenCL™ APIs. Leverage these features within your own IDEs or use the standalone Vitis IDE.

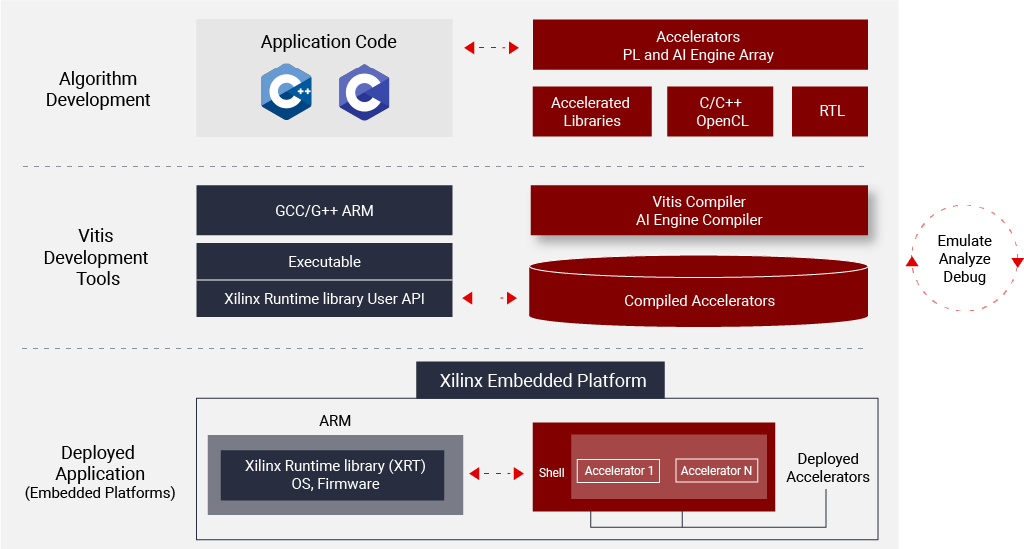

Xilinx Runtime library

The Xilinx Runtime library (XRT) facilitates communication between your application code (running on an embedded Arm or x86 host) and the accelerators deployed on the reconfigurable portion of PCIe® interface-based AMD accelerator cards, MPSoC-based embedded platforms, or adaptive SoCs. It includes user-space libraries and APIs, kernel drivers, board utilities, and firmware.

Vitis Target Platforms

The Vitis target platform defines base hardware and software architecture and application context for AMD platforms, including external memory interfaces, custom input/output interfaces, and software runtime.

•For AMD accelerator cards on premises or in the cloud, the Vitis target platform automatically configures the PCIe interfaces that connect and manage communication between your FPGA accelerators and x86 application code—you don’t need to implement any connection details!

•For AMD embedded devices, the Vitis target platform also includes the operating system for the processor on the platform, boot loader and drivers for platform peripherals, and root file system. You can use predefined Vitis target platforms for AMD evaluation boards or define your own in the Vivado™ Design Suite.

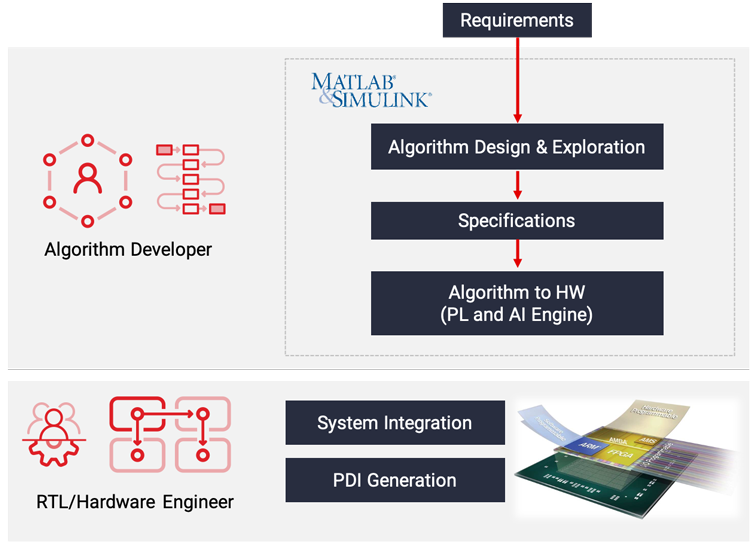

Vitis Model Composer is an AMD toolbox for the MATLAB and Simulink environment that enables rapid design exploration and verification within the MATLAB and Simulink tool and accelerates the path to production on AMD devices.

- Create a design using optimized blocks targeting AI Engines and programmable logic. Visualize and analyze simulation results and compare the output to golden references generated using the MATLAB and Simulink software.

- Seamlessly co-simulate AI Engine and programmable logic (HLS, HDL) blocks.

- Automatically generate code (AI Engine dataflow graphs, RTL, HLS C++) and test benches for a design.

- Validate your design in hardware with ease of use.

Vitis HLS

The Vitis™ HLS tool allows users to easily create complex FPGA algorithms by synthesizing a C/C++ function into RTL. The Vitis HLS tool is tightly integrated with both the Vivado™ Design Suite for synthesis and place & route and the Vitis™ unified software platform for heterogenous system designs and applications.

- Using the Vitis HLS flow, users can apply directives to the C code to create the RTL specific to a desired implementation.

- Multiple design architectures can be created from the C source code and a path for high-quality, correct-by-construction RTL is enabled.

- C simulation can be used to validate the design and allows faster iterations than a traditional RTL-based simulation.

- The Vitis HLS tool features a rich set of analysis and debugging tools that facilitate design optimization.

Using Vitis™ Software for Application Acceleration Development Flows

Design accelerators for your data and compute-intensive applications at the edge, on-premise or in the cloud:

- Identify the performance-critical portions of your application that demands acceleration.

- Design Accelerators using Vitis Accelerated libraries or develop your own in C,C++, OpenCL or RTL.

- Build, Analyze and Debug to verify functional correctness and validate performance goals are met.

- Deploy Accelerated Application on AMD Platforms at edge, on-premise or cloud.

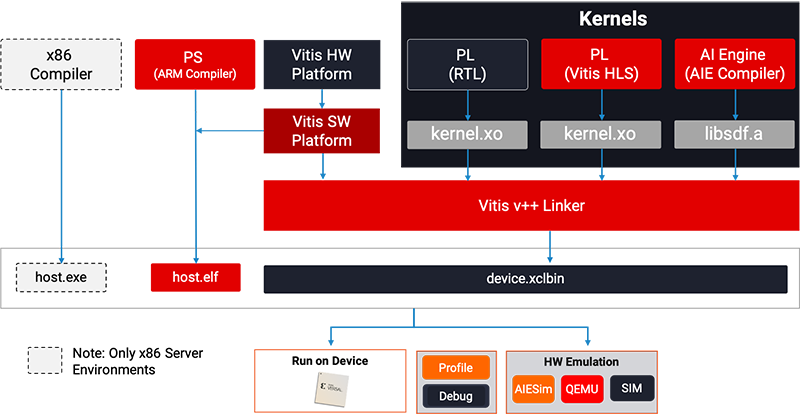

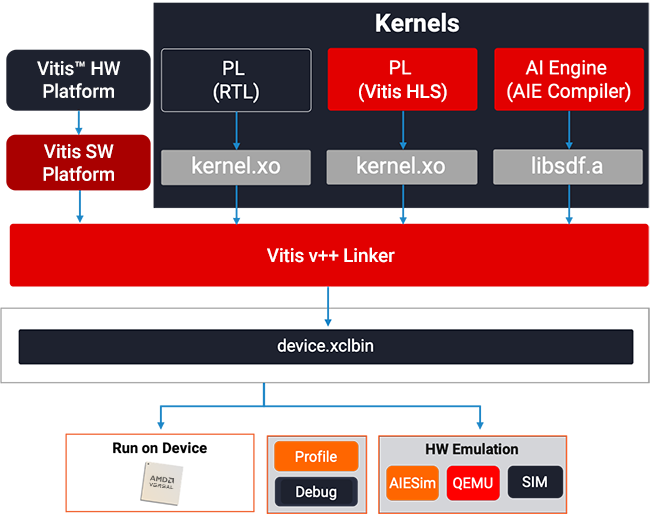

Acceleration Kernels

Vitis supports hardware acceleration kernels with PS or x86 to control kernels. The Vitis application acceleration development flow provides a framework for developing and delivering FPGA-accelerated applications using standard programming languages for both software and hardware components. For kernel creation, users can choose from the following:

- Writing traditional RTL for PL kernel

- C/C++ coding with Vitis HLS for PL kernel

- Vitis model composer for PL and/or AI Engine

- And C/C++ coding with AI Engine compiler for AI Engine

Vitis also supports hardware acceleration kernels without PS, or x86 to control for free-running. Free-running kernels have no control signal ports, and cannot be started or stopped. The "no-control signal" feature of the free-running kernel results in the following characteristics:

- The free-running kernel has no memory input or output port, therefore it interacts with the host or other kernels (other kernels can be regular kernel or another free-running kernel) only through streams.

- When the FPGA is programmed by the binary container (xclbin), the free-running kernel starts running on the FPGA, and therefore it does not need the clEnqueueTask command from the host code.

- The kernel works on the stream data as soon as it starts receiving from the host or other kernels, and it stalls when the data is not available.

Using Vitis Software for Embedded Software Development Flows

Vitis core development kit includes comprehensive developer tools to design, debug, and deploy software applications targeted towards embedded processors on AMD Zynq, MPSoC, RFSoC, and adaptive SoC devices. Vitis embedded software development features include:

- Importing target platform definition created using Vivado™ Design Suite

- Application development for single, multi-processor and heterogenous processor systems

- Ability to create and configure board support packages (BSPs) for third-party OS

- Board bring-up and Firmware development

- System-level performance analysis and benchmarking

- Real-time debug and trace of heterogeneous embedded systems

Learn More about the AMD Embedded Software Infrastructure.

Versal AI Engine Development

The AMD VCK5000 Versal™ development card is built on the AMD 7nm Versal adaptive SoC architecture designed for 5G, DC compute, AI, Signal Processing, Radar and others. The domain-specific architecture brings considerable compute horsepower while enabling software programmability. Move your applications to the next level with AI Engines and start developing in with Vitis high-level abstraction APIs and its libraries.

On-Premise Deployment

AMD Alveo™ Data Center accelerator cards are designed to meet the constantly changing needs of the modern Data Center, providing up to 90X performance increase over CPUs for common workloads, including machine learning inference, quantitative finance, video transcoding, and database search and analytics.

Vitis™ software development platform enables application, software, and hardware developers alike to leverage the power of Alveo accelerator cards to meet the demanding compute, network, and storage requirements of their applications.

Kria SOM Deployment

You can now run Certified Ubuntu Linux on the AMD Kria SOM. Learn how you can download, compile, run, and modify a wide selection of Vitis-AI examples with ease, without leaving the familiar Ubuntu environment.

Edge Development

As the data being produced continues to explode, there's a growing need to be able to bring computing power closer to the source of the data to meet the response-time, power-consumption and cost goals of performance-critical applications like IIoT, Automated Driving, Medical Imaging, Surveillance among others.

AMD embedded platforms are enabling applications where differentiation is key, power efficiency is critical, systems must be extremely responsive, and the latest algorithms and sensors need to be quickly deployed.

Blockchain Acceleration

AMD blockchain solution on Varium C1100 card is based on Vitis library, is an out-of-box blockchain solution, is integrated with world popular open-source software with C++ coding, easy to use and deployment on AMD Varium C1100 card. Bring Blockchain Solution on Varium™ C1100 card using AMD Vitis tool.

Learn More about Varium C1000 >

Learn More about Vitis Blockchain Solution >

Article: Develop with Blockchain >

Cloud Deployment

AMD Platforms are designed to meet the constantly changing needs of modern data center workloads like Deep Learning, Video Transcoding, Big Data Analytics, Genomics, Compression, Network Security & Search that require high bandwidth, enhanced networking, and very high compute capabilities over CPU and GPU alternatives while lowering the total cost of ownership.

AMD FPGAs are now broadly accessible to all developers everywhere through public cloud service providers like Amazon AWS. Using Vitis, you can leverage the power of AMD FPGAs in the cloud, while continuing to develop in familiar programming languages like C and C++. You can also publish your FPGA-accelerated applications on the broader cloud marketplace and monetize your solutions.

Vitis Unified Software Platform Documentation

The Vitis™ unified software platform documentation provides support for using Vitis for each of the two software development flows: Application acceleration development and Embedded software development.

Develop Accelerated Applications

6 steps to setup and accelerate your application using Vitis™ Unified Software Platform:

Download Software and Access Documentation and Training

- Step 1: Download the Vitis Core Development Kit

- Step 2: Download the Xilinx Runtime library (XRT)

- Step 3: Download the Vitis Accelerated Libraries from GitHub

- Step 4: Download Vitis Target Platform Files

- Step 5: Access all Vitis Documentation

- Step 6: Take a Vitis Training Course (On Demand, Virtual, or Classroom)

Develop Using Vitis in the Cloud

Develop accelerated applications with the Vitis Unified Software Platform in the Cloud – No local software installations or upfront purchase of hardware platforms necessary (pay-as-you-go). Log in and get started right away.

Access Vitis Tools using the FPGA Developer AMI, on AWS Marketplace. This AMI (Amazon Machine Instance) includes everything you need to develop, simulate, debug, and compile your accelerated algorithms on F1 instances – no local software setups required.

Vitis Target Platforms

Note: Alveo Target Platforms for 2020.1 are compatible with Vitis tools 2020.2

For instructions on how to create custom embedded target platforms for Vitis, see Vitis Embedded Software Development User Guide – UG1400